The Cost of Doing Good Business

There are methods which attempt to correct CSYNC after it is generated from either AND or XNOR logic. TB476 is an Application Note from Renesas Electronics which details a system for doing this using ICs they manufacture. The final circuit is very large and complex, and it can’t universally correct for every type of format, especially any type of interlaced content. It’s still worth a read, since it’s one of the rare resources found on the internet that actually acknowledges and corroborates that these AND/XNOR based CSYNC generators cause problems.

For systems/devices that are only expecting and targeting one type of video format, I believe it’s worth implementing the extra time, resources, and effort to make sure the end-user has a trouble-free experience by generating a proper CSYNC signal. It’s not worth the risk relying on auxiliary safetynets, such as PLL coasting or wide lock/hold ranges, that may or may not be engineered into a receiving device. Even in multi-format systems which are already generating the HSYNC and VSYNC in the first place, you should be able to additionally generate a correct CSYNC with minimal extra effort and cost instead of opting for an AND/XNOR gate. This is especially true if you have to deal with realigning pulses prior to the logic gate and then filtering out glitches on the output, which is already a bunch of additional work in the first place. Lastly, it’s worth iterating once again that none of the methods discussed in this article can handle interlaced formats in a manner that even begins to approach a reasonable level of reliability.

Summary

The main takeaways from Part 2 are as follows:

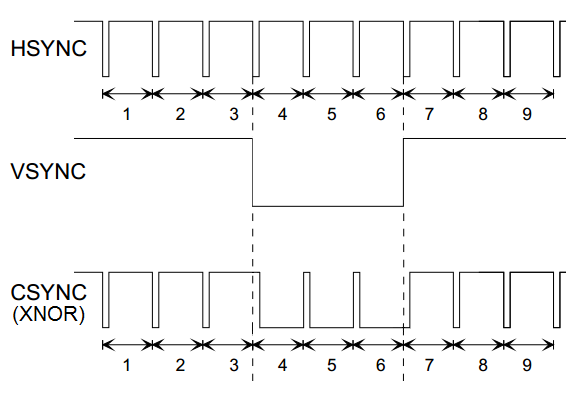

1.) AND logic is the most basic form of CSYNC generation, and it was used commonly in early progressive-based video systems.

2.) XNOR logic is a step above AND logic in terms of reliability, as long as you mitigate the creation of transition glitches.

3.) For either of these methods to work reasonably well in enough scenarios, proper widths and positional alignment are required on the input HSYNC and VSYNC signals.

4.) These two simple logic gate methods have a unique benefit where they can be used effectively in a universal system dealing with many possible input formats.

5.) Fixing CSYNC errors after generation is very costly, unreliable, and non-universal. It’s also very difficult to do for interlaced systems.

In the upcoming Part 3 of this series, I’ll try to finally tackle proper CSYNC generation. If you are familiar with digital logic, both of the methods discussed above are types of “combinational logic”. The 2nd type of logic used in digital systems is known as “sequential logic”, and it’s what we need to use to engineer a correct CSYNC output.

![[Top] CSYNC from a Sega Master System (Model 1)[Bottom] Zoomed-in version of the top](https://images.squarespace-cdn.com/content/v1/51f517f0e4b01da70d01ca2a/1571164539691-HKXPVY1CKHJVA1C3RKOK/sms_and.png)

![[Top] CSYNC from a Sega Genesis running in Master System mode[Bottom] Zoomed-in version of the top](https://images.squarespace-cdn.com/content/v1/51f517f0e4b01da70d01ca2a/1571171039769-FNH1Y6AS7DVOLJG51EX0/genesis_xnor.png)

![[Left-half] HSYNC (blue) & VSYNC (yellow) on the TurboGrafx-16 expansion port along with a direct XNOR combination of them (violet).[Right-half] Internally generated CSYNC (violet) from the TurboGrafx-16’s video processor along with the same exp…](https://images.squarespace-cdn.com/content/v1/51f517f0e4b01da70d01ca2a/1571222297220-CD0H1RA0TU92B4F65M51/tg16_csync.png)